# ОГЛАВЛЕНИЕ

| Введ  | цение                                                          | ) |

|-------|----------------------------------------------------------------|---|

| Глаг  | ва 1. Процессорное ядро ARM71                                  | 1 |

|       | Основные положения                                             |   |

|       | Конвейер                                                       |   |

|       | Регистры                                                       |   |

|       | Регистр текущего состояния программы                           |   |

|       | Режимы обработки исключительных ситуаций                       |   |

| 1.6.  | Набор команд ARM7                                              |   |

|       | 1.6.1. Команды ветвления                                       |   |

|       | 1.6.2. Команды обработки данных                                |   |

|       | Команда обмена                                                 |   |

| 1.8.  | Изменение регистров состояния                                  | 5 |

|       | Программное прерывание                                         |   |

|       | Модуль МАС                                                     |   |

|       | Набор команд THUMB                                             |   |

| 1.12. | Резюме                                                         | ) |

| Глаг  | ва 2. Разработка программного обеспечения                      | ) |

| 2.1.  | Основные положения                                             | ) |

|       | 2.1.1. Загрузка и установка пакета программ компании Кеіl 30   | ) |

|       | 2.1.2. ИСР µVISION                                             | 1 |

|       | 2.1.3. ИСР HiTOP 3.                                            | 3 |

|       | 2.1.4. Учебные примеры                                         |   |

| 2.2.  | Стартовый код                                                  |   |

|       | 2.2.1. Определение карты памяти проекта       36               |   |

|       | 2.2.2. Определение карты памяти для компилятора GCC         36 |   |

| 2.3.  | Взаимодействие кодов ARM и THUMВ                               |   |

|       | 2.3.1. Обеспечение взаимодействия в компиляторе GCC            |   |

| 2.4.  | Библиотека STDIO                                               |   |

|       | 2.4.1. Библиотека STDIO и компилятор GCC                       |   |

|       |                                                                | - |

#### 4 ■ Оглавление

| 2.5.  | Организация доступа к периферийным устройствам                          | . 45 |

|-------|-------------------------------------------------------------------------|------|

|       | 2.5.1. Организация доступа к периферийным устройствам в компиляторе GCC | . 46 |

| 2.6.  | Процедуры обработки прерываний                                          |      |

|       | 2.6.1. Обработка прерываний в компиляторе GCC                           | . 47 |

|       | 2.6.2. Отладка обработчиков системных ошибок                            | . 47 |

|       | 2.6.3. Программное прерывание                                           | . 48 |

|       | 2.6.4. Программное прерывание и компилятор GCC                          | . 50 |

|       | 2.6.5. Размещение переменных по абсолютным адресам                      | . 51 |

|       | 2.6.6. Размещение кода в ОЗУ                                            |      |

|       | 2.6.7. Загрузка кода и данных в ОЗУ при использовании компилятора GCC   | . 52 |

| 2.7.  | Встраиваемые функции                                                    |      |

|       | 2.7.1. Встраиваемые функции в компиляторе GCC                           |      |

| 2.8.  | Встроенный ассемблер                                                    |      |

|       | 2.8.1. Встроенный ассемблер компилятора GCC                             |      |

|       | 2.8.2. Импортирование программ для компилятора GCC                      |      |

| 2.9.  | Аппаратные средства отладки                                             |      |

|       | 2.9.1. Важное замечание!                                                |      |

|       | 2.9.2. Еще более важное замечание!                                      |      |

| 2.10  | . Резюме                                                                |      |

|       |                                                                         |      |

| Гпа   | ва 3. Системные периферийные устройства                                 | 60   |

| 1 114 | ва 3. Спетемпые периферинные устронетва                                 | . 00 |

| 3.1.  | Основные положения                                                      | . 60 |

| 3.2.  | Внутренние шины                                                         | . 60 |

|       | Организация памяти                                                      |      |

|       | Программирование регистров                                              |      |

| 3.5.  | Модуль ускорения работы памяти                                          |      |

|       | 3.5.1. Пример конфигурирования модуля МАМ                               |      |

| 3.6.  | Программирование FLASH-памяти                                           |      |

|       | 3.6.1. Управление картой распределения памяти                           |      |

|       | 3.6.2. Загрузчик                                                        | . 69 |

|       | 3.6.3. Внутрисхемное программирование (ISP)                             | . 71 |

|       | 3.6.4. Внутрипрограммное программирование (ІАР)                         | . 72 |

|       | 3.6.5. Защита FLASH-памяти                                              | . 73 |

|       | 3.6.6. Системные тактовые сигналы                                       | . 73 |

|       | 3.6.7. Схема ФАПЧ                                                       | . 76 |

|       | 3.6.8. Тактовые сигналы периферийных устройств                          | . 78 |

| 3.7.  | Управление электропитанием                                              | . 78 |

|       | 3.7.1. Группы потребителей                                              |      |

|       | 3.7.2. Режимы пониженного энергопотребления                             | . 79 |

| 3.8.  | Система прерываний LPC2300                                              | . 81 |

|       | 3.8.1. Блок управления выводами                                         | . 82 |

|       | 3.8.2. Выводы внешних прерываний                                        |      |

|       | 3.8.3. Структура прерываний                                             |      |

|       | 3.8.4. Прерывание FIQ                                                   |      |

|       |                                                                         |      |

| 3.9. | 3.8.5. Выход из прерывания FIQ 3.8.6. Векторные прерывания IRQ 3.8.7. Выход из прерывания IRQ 3.8.8. Пример: прерывание IRQ 3.8.9. Программное прерывание 3.8.10. Вложенные прерывания Контроллер DMA. 3.9.1. Обзор модуля DMA 3.9.2. Синхронизация DMA 3.9.3. Пересылка из памяти в память | 86 88 88 90 91 91 93 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|      | 3.9.4. Пакетная передача                                                                                                                                                                                                                                                                    |                      |

|      | 3.9.5. Поддержка модулем DMA периферийных устройств                                                                                                                                                                                                                                         |                      |

| 3 10 | 3.9.6. Пересылка несмежных данных                                                                                                                                                                                                                                                           |                      |

| 5.10 | . I CSIOME                                                                                                                                                                                                                                                                                  | 93                   |

| Гла  | ва 4. Периферийные устройства общего назначения                                                                                                                                                                                                                                             | 96                   |

| 4.1. | Основные положения                                                                                                                                                                                                                                                                          | 96                   |

| 4.2. | Порты ввода/вывода общего назначения                                                                                                                                                                                                                                                        | 96                   |

|      | 4.2.1. Быстрые регистры ввода/вывода                                                                                                                                                                                                                                                        | 96                   |

|      | 4.2.2. Прерывание от GPIO                                                                                                                                                                                                                                                                   | 99                   |

| 4.3. | Таймеры общего назначения                                                                                                                                                                                                                                                                   | 100                  |

|      | 4.3.1. Режим захвата                                                                                                                                                                                                                                                                        | 100                  |

|      | 4.3.2. Режим счетчика                                                                                                                                                                                                                                                                       |                      |

|      | 4.3.3. Режим совпадения                                                                                                                                                                                                                                                                     |                      |

| 4.4. | Модуль ШИМ                                                                                                                                                                                                                                                                                  |                      |

|      | 4.4.1. Режим счетчика                                                                                                                                                                                                                                                                       |                      |

| 4.5. | Часы реального времени                                                                                                                                                                                                                                                                      |                      |

|      | 4.5.1. Опорный сигнал модуля RTC                                                                                                                                                                                                                                                            | 111                  |

| 4.6. | Сторожевой таймер                                                                                                                                                                                                                                                                           |                      |

| 4.7  | 4.6.1. Период сторожевого таймера                                                                                                                                                                                                                                                           |                      |

| 4.7. | Универсальный асинхронный приемопередатчик                                                                                                                                                                                                                                                  |                      |

|      | 4.7.1. Настройка скорости обмена                                                                                                                                                                                                                                                            |                      |

|      | 4.7.2. Автоопределение скорости обмена                                                                                                                                                                                                                                                      |                      |

|      | 4.7.3. Передача данных                                                                                                                                                                                                                                                                      |                      |

| 4.0  | 4.7.4. Организация обмена по протоколу IrDA                                                                                                                                                                                                                                                 |                      |

|      | Интерфейс I2C                                                                                                                                                                                                                                                                               |                      |

|      | Интерфейс SPI                                                                                                                                                                                                                                                                               |                      |

|      | . Аналого-цифровой преобразователь                                                                                                                                                                                                                                                          |                      |

|      | . Синхронный последовательный порт                                                                                                                                                                                                                                                          |                      |

| 12   | 4.12.1. Контроллер I2S                                                                                                                                                                                                                                                                      |                      |

| 4.13 | . Интерфейс карт FLASH-памяти                                                                                                                                                                                                                                                               |                      |

|      | 4.13.1. Модуль МСІ микроконтроллеров семейства LPC2300                                                                                                                                                                                                                                      |                      |

| Гла  | ва 5. Развитые периферийные устройства                                  | . 150 |

|------|-------------------------------------------------------------------------|-------|

| 5.1. | Ethernet MAC                                                            | . 150 |

| 5.2. | Протокол ТСР/ІР                                                         | . 150 |

|      | 5.2.1. Сетевая модель                                                   | . 151 |

|      | 5.2.2. Ethernet и IEEE 802.3                                            | . 151 |

|      | 5.2.3. Дейтаграммы ТСР/ІР                                               | . 153 |

|      | 5.2.4. Модуль Ethernet MAC                                              |       |

|      | 5.2.5. Стек uIP                                                         | . 169 |

|      | 5.2.6. Создание веб-сервера с использованием коммерческого стека ТСР/ІР | . 173 |

| 5.3. | Полноскоростной интерфейс USB 2.0                                       | . 182 |

|      | 5.3.1. Введение в USB                                                   | . 182 |

|      | 5.3.2. Модуль контроллера USB                                           | . 196 |

|      | 5.3.3. Заключение                                                       | . 208 |

| 5.4. | Контроллер интерфейса CAN                                               | . 208 |

|      | 5.4.1. Семиуровневая модель ISO                                         | . 209 |

|      | 5.4.2. Структура узла сети CAN                                          | . 210 |

|      | 5.4.3. Объекты сообщений CAN                                            | . 211 |

|      | 5.4.4. Арбитраж на шине CAN                                             | . 213 |

|      | 5.4.5. Тактовая синхронизация                                           | . 214 |

|      | 5.4.6. Передача сообщений CAN                                           | . 216 |

|      | 5.4.7. Ограничение распространения ошибок                               | . 218 |

|      | 5.4.8. Прием сообщений CAN                                              | . 222 |

|      | 5.4.9. Фильтрация сообщений                                             | . 223 |

|      |                                                                         |       |

| Гла  | ва 6. Использование ОС компании Keil                                    | . 229 |

| 6.1. | Возможности ОСРВ.                                                       | . 229 |

|      | Настройка проекта.                                                      |       |

|      | Процессы                                                                |       |

| 6.4. | Запуск ОСРВ                                                             | . 234 |

| 6.5. | Создание процессов.                                                     | . 235 |

|      | Управление процессами                                                   |       |

|      | Множество экземпляров                                                   |       |

| 6.8. | Управление временем                                                     |       |

|      | 6.8.1. Формирование задержки                                            |       |

|      | 6.8.2. Периодический запуск процесса                                    |       |

|      | 6.8.3. Виртуальный таймер                                               | . 237 |

|      | 6.8.4. Демон ожидания                                                   |       |

| 6.9. | Межпроцессное взаимодействие                                            |       |

|      | 6.9.1. События                                                          |       |

|      | 6.9.2. Обработка прерываний в ОСРВ                                      |       |

|      | 6.9.3. Семафоры                                                         | . 241 |

|      | 6.9.4. Предостережение по поводу семафоров                              | . 242 |

|      | 6.9.5. Мьютексы                                                         | . 242 |

|      | 6.9.6. Предостережение по поводу мьютексов                     |       |

|------|----------------------------------------------------------------|-------|

| 6.10 | . Конфигурация                                                 | . 246 |

|      |                                                                |       |

| Гла  | ва 7. Использование ОС FreeRTOS                                | . 247 |

| 7.1. | Портирование ОС FreeRTOS на LPC2300                            | . 247 |

|      | 7.1.1. Тики таймера                                            | . 248 |

|      | 7.1.2. Процедура обработки прерывания от таймера               | . 249 |

|      | 7.1.3. Переключение контекста                                  |       |

|      | 7.1.4. Инициализация стека                                     |       |

|      | 7.1.5. Управление памятью                                      |       |

| 7.2. | Конфигурация FreeRTOS                                          |       |

|      | 7.2.1. Запуск FreeRTOS                                         |       |

|      | 7.2.2. Процессы                                                |       |

|      | 7.2.3. Управление процессами                                   |       |

|      | 7.2.4. Ловушка на тики                                         |       |

|      | 7.2.5. Семафоры                                                |       |

|      | 7.2.6. Управление ядром                                        |       |

|      | 7.2.0. 3 правление ядром                                       | . 201 |

| Гпо  | ва 8. Учебное пособие                                          | 262   |

| 1 Ла | BA O. 5 YEUROC HOLUUNE                                         | . 203 |

| Вве  | цение                                                          | . 263 |

| Упр  | ажнение 1. Знакомство с ИСР Кеіl                               | . 263 |

|      | Установка аппаратных средств.                                  | 263   |

|      | Отладчик Keil                                                  | . 264 |

|      | Редактирование проекта                                         | 273   |

|      | Управление процессом выполнения программы                      |       |

|      | Просмотр данных.                                               |       |

| Упр  | ажнение 2. Стартовый код                                       |       |

|      | ажнение 3. Совместное использование команд ARM и THUMB         |       |

|      | ажнение 4. Программное прерывание                              |       |

| Упр  | ажнение 5. Модуль МАМ                                          | 292   |

| Упр  | ажнение 6. Использование загрузчика от NXP                     | 293   |

| Упр  | ажнение 7. Схема ФАПЧ                                          | . 297 |

| Упр  | ажнение 8. Конфигурирование системы тактирования               | . 299 |

|      | ажнение 9. Быстрое прерывание                                  |       |

| Упр  | ажнение 10. Векторное прерывание.                              | . 304 |

|      | ажнение 11. Пересылка данных из памяти в память при помощи DMA |       |

|      | ажнение 12. Пересылка несмежных данных при помощи DMA          |       |

|      | ажнение 13. Порты ввода/вывода общего назначения               |       |

|      | ажнение 14. Прерывание от порта GPIO                           |       |

|      | ажнение 15. Функция захвата (capture)                          |       |

| _    | ажнение 16. Функция совпадения (match)                         |       |

|      | ажнение 17. ШИМ                                                |       |

| Упр  | ажнение 18. Часы реального времени                             | 316   |

#### 8 ■ Оглавление

# **ВВЕДЕНИЕ**

Эта книга представляет собой практическое руководство для тех, кто собирается использовать в своих новых разработках те или иные микроконтроллеры семейств LPC2300 и LPC2400 компании NXP Semiconductors. Данная книга не является ни справочником, ни учебным пособием. Предполагается, что читатель имеет некоторый опыт в области программирования микроконтроллеров для встраиваемых систем и знаком с языком программирования Си. Основной объем технической информации содержится в четырех первых главах книги, поэтому если вы совершенно не знакомы с семействами LPC2300/2400 и, в частности, с процессорным ядром ARM7, вам необходимо внимательно прочитать эти главы. Обращаю ваше внимание, что в книге речь пойдет, в основном, о семействе LPC2300, а особенности, присущие семейству LPC2400, будут отмечены особо.

В первой главе рассматриваются основные характеристики процессорного ядра (ЦПУ) ARM7. После прочтения этой главы вы будете знать достаточно, чтобы начать писать программы для любых устройств, построенных на базе ядра ARM7. Если же вы хотите расширить свои знания, к вашим услугам имеется несколько прекрасных книг, описывающих эту архитектуру, часть из которых указана в списке литературы. Во второй главе рассказывается о том, как следует писать программы на языке Си для процессора ARM7. По существу, в этой главе описываются специфические расширения стандарта ANSI C, требуемые для программирования встраиваемых систем. Все примеры, встречающиеся в книге, были написаны с использованием коммерческого компилятора, однако в настоящее время на платформу ARM перенесен и бесплатный пакет программ GCC.

После прочтения первых двух глав книги вы должны хорошо разбираться в процессоре и средствах разработки для него. Третья глава посвящена системной периферии семейства LPC2300. В ней рассказывается о системной архитектуре микроконтроллеров семейства и рассматривается вопрос конфигурирования микросхем для достижения наибольшей производительности. В четвертой главе мы познакомимся со встроенными периферийными устройствами этих микроконтроллеров и узнаем, как их необходимо конфигурировать при использовании в своих программах. В пятой главе описываются более сложные периферийные устройства, такие как контроллер USB и контроллер Ethernet. Шестая и седьмая главы книги посвящены двум популярным операционным системам реального

времени для микроконтроллеров с ядром ARM — платной, разработки компании Keil, и бесплатной FreeRTOS.

На протяжении всей книги вам будут встречаться различные упражнения, которые подробно рассматриваются в восьмой главе, посвященной практическим занятиям. Все эти упражнения можно выполнить, используя ознакомительные версии компилятора и симулятора, имеющиеся на компакт-диске, который прилагается к книге. В продаже также имеется недорогой стартовый набор разработчика (starter kit), используя который вы можете загрузить учебную программу в реальный микроконтроллер и удостовериться, что она действительно работает. Я искренне надеюсь, что, читая эту книгу и выполняя упражнения, вы быстро освоите микроконтроллеры семейств LPC2300 и LPC2400.

# ПРОЦЕССОРНОЕ ЯДРО ARM7

### 1.1. Основные положения

Все микроконтроллеры семейства LPC2300 построены на основе ЦПУ ARM7. Вообще говоря, чтобы использовать эти микроконтроллеры, вам совершенно не нужно быть экспертом в области программирования процессора ARM7, поскольку заботу о большинстве сложных моментов берет на себя компилятор языка Си. Тем не менее, чтобы разработать надежное устройство, вы должны иметь хотя бы общее представление о том, как работает ЦПУ и какие у него имеются особенности.

В этой главе мы рассмотрим основные характеристики ядра ARM7 вместе с его моделью программирования, а также обсудим набор команд, используемый данным процессором. В результате вы получите всю необходимую информацию о процессоре, являющемся «сердцем» семейства LPC2300. Для более углубленного изучения процессоров ARM рекомендую обратиться к книгам, указанным в списке литературы.

Ключевой принцип, лежащий в основе процессора ARM, — простота. Ядро ARM7 является RISC-машиной, предполагающей использование небольшого числа команд и соответственно состоящей из относительно небольшого количества логических элементов. Благодаря этому процессор ARM7 идеально подходит для использования во встраиваемых системах. Он имеет высокую производительность, низкое энергопотребление и занимает небольшую часть общей площади кристалла.

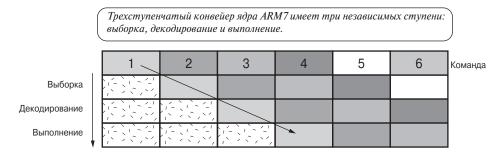

## 1.2. Конвейер

Основной элемент ЦПУ ARM7 — конвейер команд, который используется для обработки команд, считанных из памяти программ. Конкретно, в ядре ARM7 реализован трехступенчатый конвейер (**Puc. 1.1**).

Трехступенчатый конвейер является самой простой разновидностью конвейеров и не подвержен возникновению различных опасных ситуаций, таких как «чтение раньше записи», которые встречаются в конвейерах с большим числом ступеней. Конвейер имеет три аппаратно-независимые ступени, благодаря кото-

**Рис. 1.1.** Работа трехступенчатого конвейера.

рым одновременно с выполнением одной команды осуществляется декодирование второй и выборка третьей. Он настолько эффективно ускоряет прохождение команд через ЦПУ, что большинство команд ARM может выполняться за один такт. Конвейер наиболее эффективен при выполнении линейного кода. При обнаружении перехода конвейер сбрасывается, и для возобновления выполнения программы с максимальной скоростью он должен сначала заполниться. Позже мы с вами увидим, что набор команд процессора ARM имеет несколько интересных особенностей, позволяющих исключить из кода короткие переходы для улучшения прохождения кода по конвейеру. Поскольку конвейер является составной частью ЦПУ, он полностью скрыт от программиста. Тем не менее, важно помнить, что значение счетчика команд (Program Counter — PC) на 8 байт превышает значение адреса текущей выполняемой команды. В связи с этим необходимо аккуратно подходить к вычислению смещений в случае относительной адресации с использованием счетчика команд.

#### Например, команда:

0x40000 LDR PC, [PC, #4]

загрузит в счетчик команд PC содержимое, находящееся по адресу PC + 4. Поскольку PC опережает текущую команду на 8 байт, в него будет загружено содержимое по адресу 0x400C, а не 0x4004.

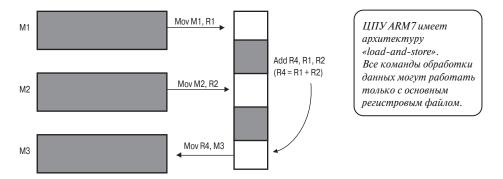

## 1.3. Регистры

Процессор ARM7 имеет архитектуру «load-and-store» (загрузка — сохранение), поэтому для выполнения любой обработки данных необходимо сначала перенести эти данные из памяти в определенные регистры, выполнить команду обработки данных и затем записать полученные значения обратно в память (**Puc. 1.2**).

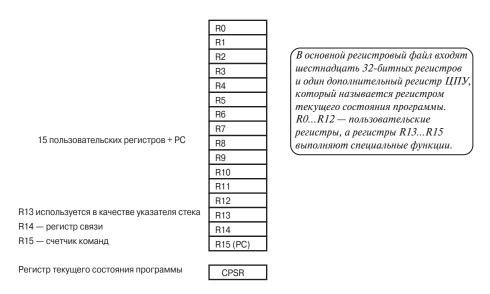

Основной регистровый файл состоит из 16 пользовательских регистров R0...R15 (**Рис. 1.3**). Каждый из этих регистров является 32-битным 10.

<sup>1)</sup> В отечественной литературе принято пользоваться понятиями «разряд», «разрядный». Двоичный разряд — это бит. В данном издании мы будем придерживаться зарубежной терминологии («бит», «битный»), что более соответствует современной тенденции в цифровой технике. — *Примеч. пер.*

Рис. 1.2. Обработка данных.

Рис. 1.3. Структура основного регистрового файла.

R0...R12 предназначены исключительно для нужд пользователя и не выполняют никаких других функций, в то время как регистры R13...R15 имеют дополнительные функции. Регистр R13 используется в качестве указателя стека (Stack Pointer — SP). Регистр R14 называется регистром связи (Link Register — LR). При вызове подпрограммы адрес возврата автоматически запоминается в регистре связи, откуда затем считывается при возврате. Такое решение позволяет быстро переходить к «концевым» функциям (функции, которые не вызывают других функций) и возвращаться из них. Если же функция входит в состав «ветви», т.е. вызывает другие функции, содержимое регистра связи необходимо сохранять в стеке (R13). Наконец, регистр R15 выполняет функции счетчика команд (PC). Что интересно, многие команды могут работать с регистрами R13...R15, как с обычными пользовательскими регистрами.

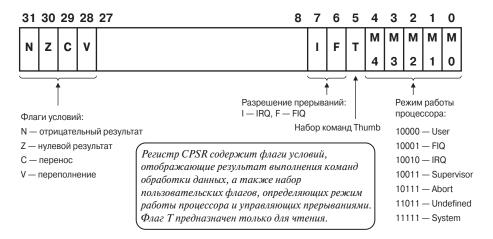

## 1.4. Регистр текущего состояния программы

Наряду с банком регистров в ЦПУ имеется дополнительный 32-битный регистр, который называется регистром текущего состояния программы (Current Program Status Register — CPSR). Регистр CPSR содержит набор флагов, которые управляют функционированием ЦПУ ARM7 и отображают его состояние (Рис. 1.4).

Рис. 1.4. Регистр текущего состояния программы.

В старших четырех битах регистра CPSR хранятся флаги условий, значения которых определяются процессором. Эти флаги отражают результат выполнения очередной команды обработки данных. Благодаря им вы можете узнать, не было ли получено в результате выполнения команды отрицательное или нулевое значение, а также не произошел ли перенос или переполнение. Младшие восемь битов регистра CPSR содержат флаги, значения которых прикладная программа может изменять. Биты 7 и 8 являются флагами I и F соответственно. Эти флаги используются для разрешения и запрещения двух линий прерываний, являющихся внешними по отношению к ЦПУ ARM7. Как мы с вами увидим позже, все периферийные модули микроконтроллеров LPC2300 подключены к этим двум линиям прерываний. При работе с данными битами нужно соблюдать осторожность, поскольку для запрещения любого из источников прерываний в соответствующий бит необходимо записать 1, а не 0, как можно было бы предположить. Пятый бит регистра является флагом THUMB.

ЦПУ ARM7 поддерживает два набора команд — 32-битный набор команд ARM и 16-битный набор команд THUMB. Соответственно флаг T показывает, какой из наборов команд используется. Учтите, что программа не должна пытаться напрямую устанавливать или сбрасывать этот флаг для переключения между наборами команд. Корректный механизм смены текущего набора команд мы рассмотрим чуть позже. Последние пять битов регистра CPSR являются флагами режима. В общей сложности процессор ARM7 поддерживает 7 режимов работы.

Прикладные программы, как правило, выполняются в режиме User. В этом режиме программа может обращаться к регистрам R0...R15 и CPSR. Однако при возникновении исключительных ситуаций (таких как прерывание, ошибка памяти или выполнение команды генерации программного прерывания) режим работы процессора изменяется. При этом регистры R0...R12 и R15 остаются теми же самыми, а регистры R13 (SP) и R14 (LR) заменяются новой парой регистров, уникальной для каждого режима. Таким образом, каждый режим имеет собственные регистр связи и указатель стека. Более того, в режиме быстрых прерываний (FIQ) дублируются и регистры R7...R12. Это позволит вам сразу же приступить к обработке прерывания FIQ, не тратя время на сохранение регистров в стеке.

В каждом из режимов, за исключением режима User, имеется дополнительный регистр, называемый регистром сохраненного состояния программы (Saved Program Status Register — SPSR). Если в момент возникновения исключительной ситуации программа находилась в режиме User, происходит смена режима и текущее содержимое регистра CPSR сохраняется в регистре SPSR. После обработки исключительной ситуации (при возврате из обработчика) содержимое регистра CPSR восстанавливается из SPSR, обеспечивая возобновление выполнения прикладной программы. Режимы работы процессора показаны на Рис. 1.5.

ИПУ ARM7 имеет 6 различных рабочих режимов, которые используются для обработки исключительных ситуаций. Затененные регистры представляют собой дублирующие регистры, которые «включаются» при изменении режима работы. Perucmp SPSR используется для сохранения содержимого регистра CPSR при переключении режимов.

| System & User | FIQ      | Supervisor | Abort    | IRQ      | Undefined |

|---------------|----------|------------|----------|----------|-----------|

| R0            | R0       | R0         | R0       | R0       | R0        |

| R1            | R1       | R1         | R1       | R1       | R1        |

| R2            | R2       | R2         | R2       | R2       | R2        |

| R3            | R3       | R3         | R3       | R3       | R3        |

| R4            | R4       | R4         | R4       | R4       | R4        |

| R5            | R5       | R5         | R5       | R5       | R5        |

| R6            | R6       | R6         | R6       | R6       | R6        |

| R7            | R7_fig   | R7         | R7       | R7       | R7        |

| R8            | R8_fig   | R8         | R8       | R8       | R8        |

| R9            | R9_fig   | R9         | R9       | R9       | R9        |

| R10           | R10_fig  | R10        | R10      | R10      | R10       |

| R11           | R11_fig  | R11        | R11      | R11      | R11       |

| R12           | R12_fig  | R12        | R12      | R12      | R12       |

| R13           | R13_fig  | R13_svc    | R13_abt  | R13_irq  | R13_und   |

| R14           | R14_fig  | R14_svc    | R14_abt  | R14_irq  | R14_und   |

| R15 (PC)      | R15 (PC) | R15 (PC)   | R15 (PC) | R15 (PC) | R15 (PC)  |

|               |          |            |          |          |           |

| CPSR          | CPSR     | CPSR       | CPSR     | CPSR     | CPSR      |

|               | SPSR_fig | SPSR_svc   | SPSR_abt | SPSR_irq | SPSR_und  |

*Рис. 1.5.* Режимы работы процессора.

## 1.5. Режимы обработки исключительных ситуаций

При возникновении исключительной ситуации изменяется режим работы ЦПУ, и в РС загружается адрес соответствующего вектора прерывания (**Табл. 1.1**). Таблица векторов начинается с нулевого адреса, первым в таблице расположен вектор сброса, а за ним остальные векторы (по 4 байта на каждый).

Таблица 1.1. Адреса векторов прерываний

| Исключительная ситуация                                        | Режим      | Адрес вектора |

|----------------------------------------------------------------|------------|---------------|

| Reset (сброс)                                                  | Supervisor | 0x00000000    |

| Undefined instruction (неопределенная команда)                 | Undefined  | 0x00000004    |

| SWI (программное прерывание)                                   | Supervisor | 0x00000008    |

| Prefetch Abort (ошибка обращения к памяти при выборке команды) | Abort      | 0x0000000C    |

| Data Abort (ошибка обращения к памяти при доступе к данным)    | Abort      | 0x00000010    |

| IRQ (прерывание)                                               | IRQ        | 0x00000018    |

| FIQ (быстрое прерывание)                                       | FIQ        | 0x0000001C    |

Каждому режиму работы соответствует свой вектор прерывания. При смене процессором режима производится переход по этому вектору. Обратите внимание! Вектор по адресу 0х00000014 отсутствуeт!

Замечание. В таблице векторов имеется «дырка», поскольку вектор с адресом 0x00000014 отсутствует. Этот адрес использовался в ранних версиях процессоров ARM, а в процессоре ARM7 он сохранен, чтобы обеспечить программную совместимость между различными архитектурами ARM. Однако, как мы увидим позже, в микроконтроллерах семейства LPC2300, эти четыре байта играют очень важную роль.

При одновременном возникновении нескольких исключительных ситуаций используется метод приоритетов. Приоритеты прерываний приведены в **Табл. 1.2**.

Таблица 1.2. Приоритеты прерываний

| Приоритет | Исключительная ситуация   |

|-----------|---------------------------|

| Высший 1  | Reset                     |

| 2         | Data Abort                |

| 3         | FIQ                       |

| 4         | IRQ                       |

| 5         | Prefetch Abort            |

| Низший 6  | Undefined instruction SWI |

Каждый источник исключительной ситуации имеет фиксированный приоритет. Встроенные периферийные устройства обслуживаются прерываниями FIQ и IRQ. Приоритеты прерываний от периферийных устройств можно назначать внутри этих групп.

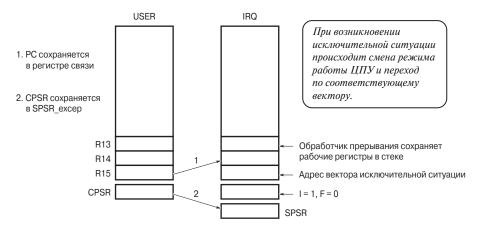

Когда возникает исключительная ситуация, например, прерывание IRQ, процессор выполняет следующие действия (**Puc. 1.6**). Во-первых, адрес следующей выполняемой команды (PC + 4) сохраняется в регистре связи. Затем регистр CPSR копируется в регистр SPSR конечного режима (в нашем случае SPSR\_irq). После этого в PC заносится адрес вектора прерывания режима исключительной ситуации. Для режима IRQ этот адрес — 0x00000018. В то же время режим работы процессора меняется на IRQ, в результате чего регистры R13 и R14 заменяются соответствующими регистрами этого режима. При входе в режим IRQ устанавливается флаг I регистра CPSR, что приводит к отключению линии IRQ. Если требуется использовать вложенные прерывания, то вы должны вручную разрешить

прерывание IRQ в программе и занести содержимое регистра связи в стек, чтобы сохранить исходный адрес возврата. С вектора прерывания программа перейдет к выполнению подпрограммы обработки прерываний. Первое, что необходимо сделать в этой подпрограмме, — сохранить в стеке IRQ все регистры из диапазона R0...R12, которые будут в ней использоваться. Затем можно приступать собственно к обработке исключительной ситуации.

Рис. 1.6. Обработка исключительной ситуации.

После завершения обработки исключительной ситуации необходимо вернуться в режим User и продолжить выполнение программы с прерванного места. Однако в наборе команд ARM отсутствуют команды типа «возврат» или «возврат из подпрограммы», поэтому манипуляции со счетчиком команд PC необходимо осуществлять, используя обычные команды. Ситуация осложняется тем, что существует несколько различных вариантов возврата.

Для начала взглянем на команду SWI. При выполнении этой команды адрес следующей выполняемой команды сохраняется в регистре связи, после чего производится обработка исключительной ситуации. Все, что нам нужно сделать для возврата из исключительной ситуации, — это загрузить содержимое регистра связи обратно в РС, и программа продолжит свое выполнение. Однако чтобы ЦПУ при этом переключился обратно в режим User, необходимо использовать специальную команду пересылки MOVS (более подробно мы рассмотрим ее чуть позже). Таким образом, команда возврата из программного прерывания будет следуюшей:

MOVS : Скопировать регистр связи в РС и переключить режимы R15, R14

А при возникновении исключительной ситуации по прерываниям FIQ и IRQ текущая выполняемая команда сбрасывается и выполняется переход к обработчику исключительной ситуации. При возврате из исключительной ситуации в регистре связи находится адрес отброшенной команды плюс 4. Чтобы возобновить выполнение программы с нужного места, мы должны уменьшить значение, хранящееся в регистре связи, на 4. В данном случае для уменьшения содержимого регистра связи и сохранения результата в PC мы используем специальную команду вычитания, восстанавливающую также и режим работы ЦПУ. Таким образом, команда возврата из режимов FIQ, IRQ и Abort выглядит следующим образом:

SUBS R15, R14, #4

В случае, если произошла ошибка обращения к памяти, исключительная ситуация возникнет через одну команду после той, выполнение которой явилось ее причиной. В идеале, в этом случае мы должны перейти к подпрограмме обработки прерывания Data Abort, выяснить и устранить причину затруднений и снова попытаться выполнить команду, вызвавшую исключительную ситуацию. Соответственно, мы должны «отмотать» РС назад на две команды — отброшенную и вызвавшую возникновение исключительной ситуации. Другими словами, нам нужно вычесть из регистра связи число восемь и сохранить результат в РС. Таким образом, команда возврата из прерывания Data Abort имеет вид:

SUBS R15, R14, #8

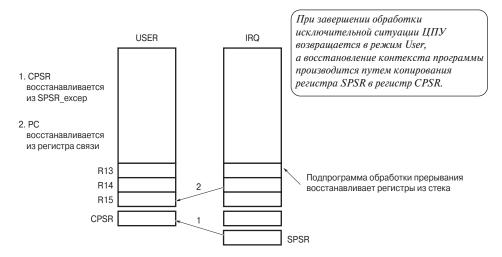

При выполнении команды возврата модифицированное содержимое регистра связи загружается в счетчик команд, ЦПУ переключается обратно в режим User, а содержимое регистра SPSR переписывается обратно в CPSR. В случае возникновения исключительных ситуаций FIQ или IRQ дополнительно разрешаются соответствующие прерывания. В результате всех этих действий процессор выходит из привилегированного режима и возвращается к выполнению пользовательской программы (Рис. 1.7).

*Рис.* 1.7. Завершение обработки исключительной ситуации.

## 1.6. Набор команд ARM7

Теперь, когда мы получили общее представление о ядре ARM7, его модели программирования и режимах работы, пришла пора познакомиться с его набором или, точнее, наборами команд. Поскольку все примеры в книге написаны на

Си, вам нет необходимости быть экспертом в области программирования на ассемблере ARM7. Однако чтобы разрабатывать действительно эффективные программы, очень важно понимать машинный код, скрывающийся за строками программы на языке высокого уровня. Прежде чем мы приступим к изучению команд ARM7, необходимо отметить, что на самом деле ЦПУ ARM7 поддерживает два набора команд: набор команд ARM с 32-битными командами и набор команд THUMB с 16-битными командами. Далее в книге слово ARM будет означать 32битный набор команд, а слово ARM7 — собственно ЦПУ.

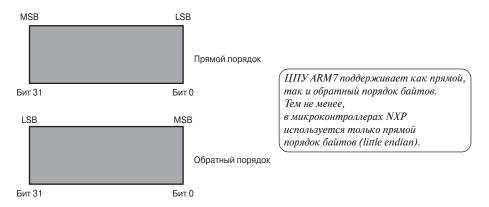

Ядро ARM7 было разработано таким образом, чтобы его можно было использовать как в качестве процессора с обратным порядком байтов (big-endian processor), так и в качестве процессора с прямым порядком байтов (little-endian processor). В первом случае старший бит (Most Significant Bit — MSB) 32-битного слова располагается в начале слова, а во втором случае — в конце (Рис. 1.8). Думаю, вы обрадуетесь, узнав, что в семействе LPC2300 используется только прямой порядок байтов (т.е. MSB является битом с самым старшим адресом), что значительно облегчает работу с процессором. Однако используемый вами компилятор для ARM7 должен уметь компилировать код в обоих форматах. В связи с этим необходимо удостовериться, что формат слов задан правильно, в противном случае полученный код будет «вывернут наизнанку».

**Рис. 1.8.** Прямой и обратный порядок байтов.

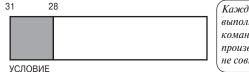

Одна из наиболее интересных особенностей набора команд ARM заключается в том, что каждая команда поддерживает условное выполнение. В традиционных микроконтроллерах единственными условными командами являются команды условных переходов, и, быть может, ряд других, таких как команды проверки либо изменения состояния отдельных битов. А в наборе команд ARM старшие 4 бита кода команды всегда сравниваются с флагами условий в регистре CPSR (Рис. 1.9). Если их значения не совпадают, команда не выполняется и проходит через конвейер как команда NOP (нет операции).

Таким образом, можно выполнить какую-либо команду обработки данных, изменяющую флаги условий в регистре CPSR. Затем, в зависимости от результата, следующая команда может быть выполнена, а может и нет. К базовым мнемо-

Каждая команда ARM (32-битная) является условно выполняемой. Между 4 старшими битами кода команды и флагами условий регистра CPSR производится операция «Логическое И». Если значения не совпадают, выполняется команда NOP.

*Рис.* 1.9. Расположение битов сравнения в команде ARM.

ническим обозначениям команд ассемблера, таким как MOV или ADD, можно добавить любой из шестнадцати префиксов, определяющих тестируемые состояния флагов условий (**Табл. 1.3**).

Таблица 1.3. Префиксы команд

| Префикс | Флаги                           | Значение                     |

|---------|---------------------------------|------------------------------|

| EQ      | Z установлен                    | Равно                        |

| NE      | Z сброшен                       | Не равно                     |

| CS      | С установлен                    | Выше или равно (беззнаковое) |

| CC      | С сброшен                       | Ниже (беззнаковое)           |

| MI      | N установлен                    | Отрицательный результат      |

| PL      | N сброшен                       | Положительный результат      |

| VS      | V установлен                    | Переполнение                 |

| VC      | V сброшен                       | Нет переполнения             |

| HI      | С установлен, Z сброшен         | Выше (беззнаковое)           |

| LS      | С сброшен, Z установлен         | Ниже или равно (беззнаковое) |

| GE      | N равен V                       | Больше или равно (знаковое)  |

| LT      | N не равен V                    | Меньше (знаковое)            |

| GT      | Z сброшен И (N равен V)         | Больше (знаковое)            |

| LE      | Z установлен ИЛИ (N не равен V) | Меньше или равно (знаковое)  |

| AL      | (игнорируются)                  | Безусловное выполнение       |

К обозначению любой команды ARM (32-бит-ной) можно добавить один из 16 префиксов, определяющих тестируемые флаги условий. Соответственно, существует 16 вариантов каждой команды

#### К примеру, команда:

EQMOV R1, #0x00800000

выполнит загрузку числа 0x00800000 в регистр R1 только в том случае, если результат выполнения последней команды обработки данных был «равно» и соответственно установлен флаг Z регистра CPSR. Целью такого условного выполнения команд является обеспечение непрерывности потока команд через конвейер, так как при каждом выполнении команд перехода конвейер сбрасывается и на его повторное заполнение требуется время, что резко снижает общую производительность. На практике существует некоторый порог, при котором принудительное «проталкивание» команд NOP через конвейер оказывается эффективнее выполнения традиционных команд условного перехода и связанного с этим повторным заполнением буфера. Указанный порог равен трем командам, поэтому короткий переход, такой как:

```

if(x < 100)

X++:

```

при использовании условно-выполняемых команд ARM будет реализован более эффективно.

Все множество команд ARM можно разбить на 6 основных групп: команды ветвления, команды обработки данных, команды передачи данных, команды передачи блоков данных, команды умножения и команда программного прерывания.

#### 1.6.1. Команды ветвления

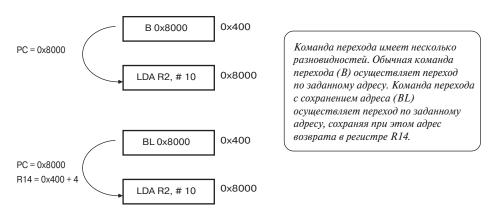

Базовая команда перехода (В), как следует из ее названия, позволяет выполнять переход в диапазоне до 32 Мбайт как вперед, так и назад. Модифицированная версия команды, команда перехода с сохранением адреса (BL), выполняет ту же операцию, однако при этом сохраняет в регистре связи текущее значение РС, увеличенное на четыре (Рис. 1.10).

**Рис. 1.10.** Команды перехода В и ВL.

Таким образом, команда перехода с сохранением адреса используется в качестве команды вызова подпрограмм, сохраняющей адрес возврата в регистре связи. Для возврата из подпрограмм можно использовать команду обычного перехода, выполняющую переход по адресу, находящемуся в регистре связи. Используя флаги условий, мы можем выполнять условные переходы и условные вызовы подпрограмм. Существует еще две разновидности команды перехода: «переход со сменой состояния» (ВХ) и «переход со сменой состояния и сохранением адреса» (BLX). Эти команды выполняют те же операции, что и предыдущие команды, но при этом еще и выполняют переключение с набора команд ARM на THUMB и обратно (Рис. 1.11).

# Конец ознакомительного фрагмента. Приобрести книгу можно в интернет-магазине «Электронный универс» e-Univers.ru